On the previous tutorial, I was presented how the Register

Transfer Level (RTL) designs methodology is successful to design a GreatestCommon Divisor (GCD) core engine.

Here again the same method I would like to apply it into

sequential multiplier unit. In the book

“Fundamentals of Digital Logic with VHDL Design” by Stephen Brown & Zvonko

Vranesic, they also provide one example to design this sequential multiplier.

However they name it as Shift-and-Add Multiplier.

Let’ me start with design

specification.

We are going to design a multiplier to multiply two an 8-bit

unsigned numbers to produces 16-bit product. For example 8-bit Data A multiply

with 8-bit Data B and produce 16-bit Product.

Algorithmic

modelling

In this step, we can translate the design specification to

produce the behavioural model of the multiplier. This model is expressed in

terms of an algorithm as shown in Figure 1, and this should be completed with

IO Block diagram of the top-level system as shown in Figure 2.

Figure 1:

Algorithm in Psedo-Code for sequential Multiplier for 8-bit input (n=8)

Figure 2:

Top-Level of Sequential Multiplier

RTL Modelling

The RTL Model is first provided in the form of an ASM

flowchart as shown in Figure 3. Then from the ASM flowchart, we can construct

the RTL control sequence table in the form of an RTL Code is derived as shown

in Table 1.

Figure 3: the ASM

Flowchart of Sequential Multiplier

Table 1: The

RTL-CS Table

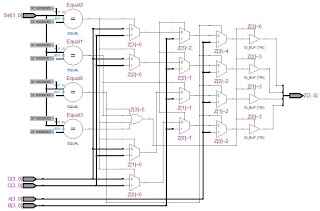

Datapath

Figure 4 shows the datapath circuit for the sequential

multiplier. The datapath consist of two shift registers, namely shift-left

register for data A and shift-right register for data B. Other components are

adder, multiplexer and register to store the Product (result).

Figure 4:

Datapath of Sequential Multiplier

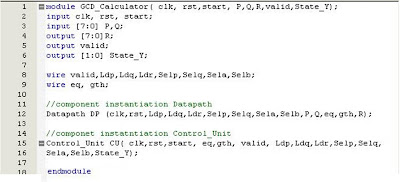

Meanwhile Figure 5 shows the top level datapath using

Verilog code.

Figure 5: A

Verilog Datapath code

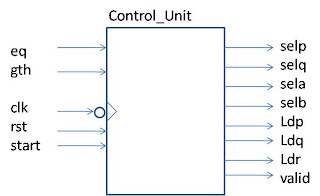

Control Unit

The Verilog program in figure 6 shows how the control unit

is constructing using Moore Model. There are three separate blocks, Next-State

Logic block, State Register block and Output Logic block.

Figure 6: Verilog

Code for Control Unit Sequential Multiplier

Waveform Simulation

Figure 7 show example waveform simulation to perform

multiplication of hexadecimal number of FFh multiply with FFh. The product

should be FE01h. In decimal number represents 255 x 255 = 65025. Inputs A and B

are define as FF hexadecimal respectively. The sequential multiplier will be

start the processing the data according to control unit. You can verify the

state movement by State_Y output. Signal output valid will be asserted in state

S3 to indicate the process of multiplication is finish and the valid result (output

R) should be taken at the same clock. The state resume again at state S0. As you can see for the worst case (FFh xFFh)

the result should be ready around 18 clock cycles compare if I want to multiply

3 x 2 which is take only 5 cycles as shown in Figure 8.

Figure 7: Output

Waveform Simulation for test vector FFh x FFh

Figure 8: Output

Waveform Simulation for test vector 3h x 2h

Can you estimate the total clock cycles required if I would

like to multiply Data A =00h with Data B= FFh ? It’s there are redundant clock

have been waste? Can you do some improvement on this design? Please provide

your feedback here!